AXIS协议学习记录-1

AXIS协议学习记录-1

AXIS基本概念

传输过程

简单的两拍握手协议,简单的数据流通信(stream),规范的要求中大部分信号都是非必须的,复杂功能需要多种实体components参与。

当TVALID与TREADY都置位(asserted)时完成一次Transfer。

数据单元分级

- Byte,AXIS的最小数据单元为字节

- Transfer,一次传输事件,对应位宽数据量。对应一组TVALID和TREADY的两拍握手

- Packet,传输任意量的字节,由Transfer组成,其中Transfer对应的所有数据为了保持对齐,可包含NULL字节。Packet对应了一次TLAST事件(TLAST指明Packet的边界),Packet与AXI的Butst类似。

- Frame,包含数个Packet。

数据字节类型

- Data byte,传输数据。

- Position byte,占位符,标识相对位置,需要搭配TSTRB信号使用。

- Null byte,用于对齐的inserted byte。通过TKEEP信号标识。

Interconnect

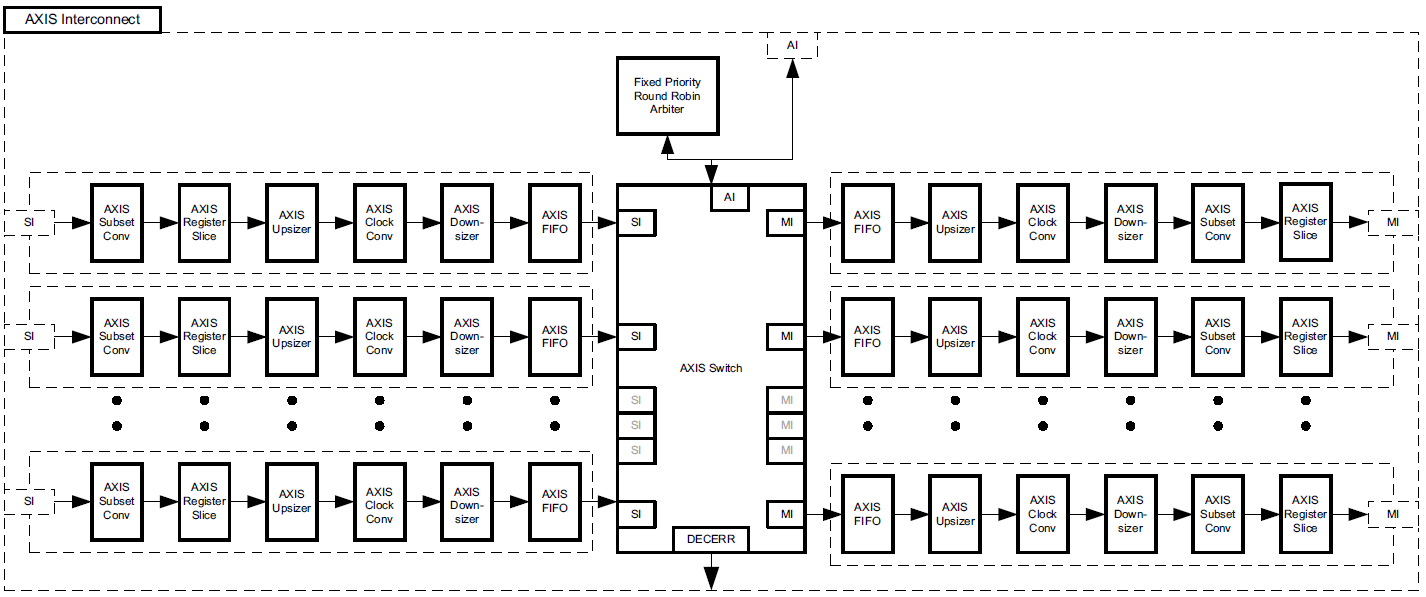

AXIS中的设备主要为Interconnect和Transimitter和Receiver组成,Interconnect实现了所有的总线管理需求,通常可以使用子模块单独完成某些功能。VIVADO IP核中AXIS Interconnect结构图示如下,图源VIVADO文档PG035

Interconnect

用于连接多个Transimitter和Receiver,可以进行数据的upsizing、downsizing,merging等,主要负责管理总线,进行总线的仲裁。为各个设备提供独立的接口,集成位宽转化。Switch

与Interconnect类似,连接多个Transimitter和Receiver,可以进行总线仲裁,但各个接口保持一致,不对数据进行处理,Interconnect的子集。Subset Conveter(Xilinx Vivado Repository)或 adapter

进行两个AXIS接口的转化,主要进行数据核控制信号的位宽变化等。CLK Converter

AXIS通信过程仅是简单的两拍握手,仅在同一时钟域内可以保证通信,若要进行不同时钟域的通信需要使用Clock Converter来匹配时钟域,如低速到高速延迟数据传输,高速到低速使用异步FIFO缓存数据。

其他模块

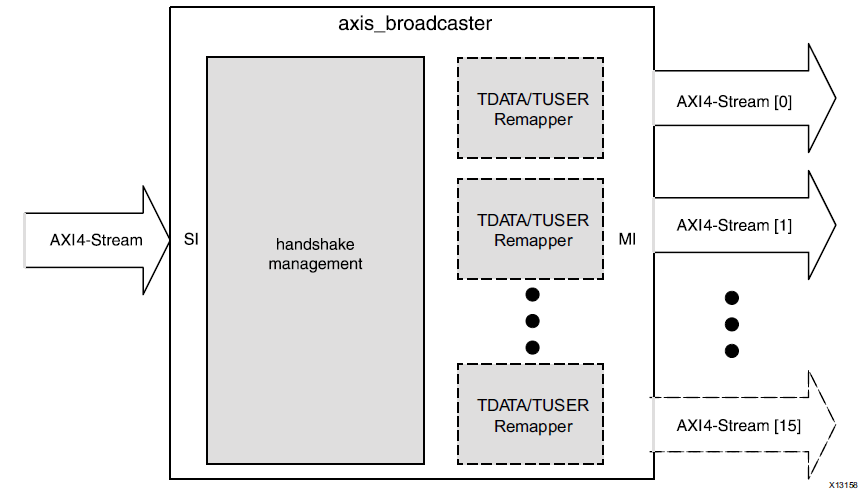

Broadcaster

实现一对多的AXIS接口复用。(一个Slave接口对应多个Master接口)。因为AXIS信号包含TDEST和TID信号,没有办法直接进行广播操作,需要借助独立模块实现该功能。

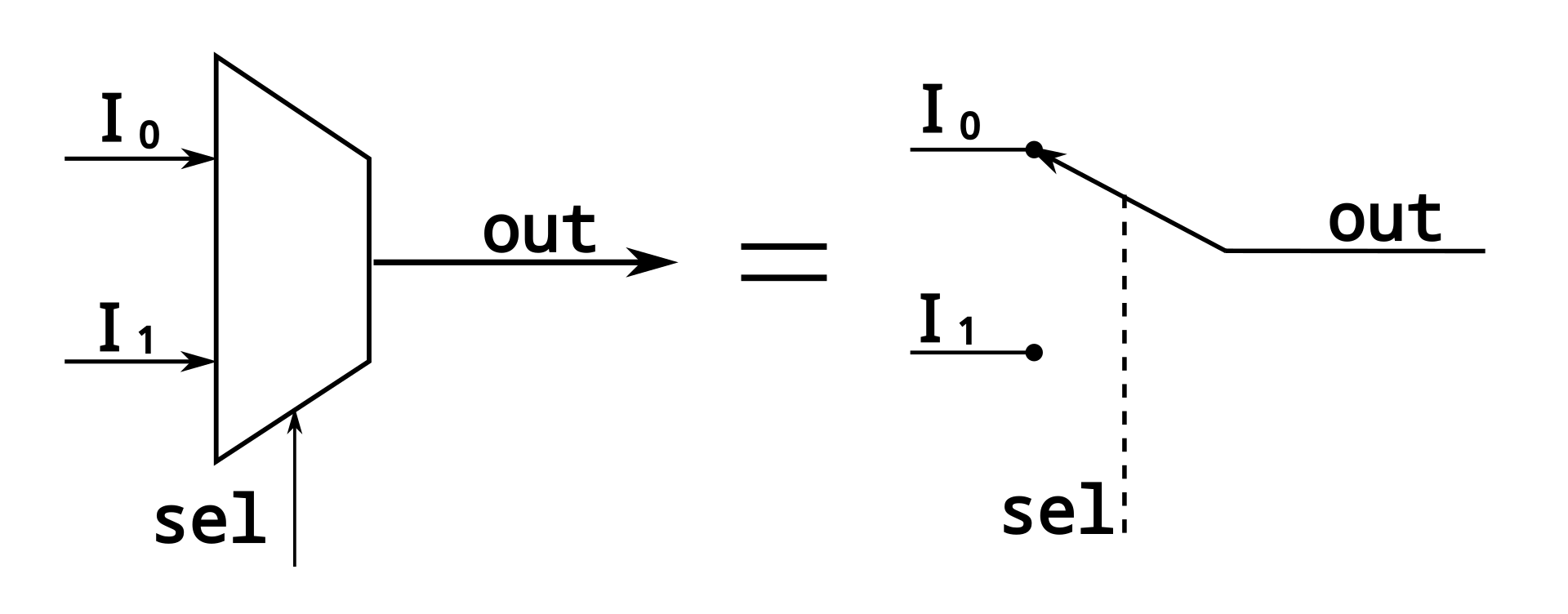

mux

multiplexer,多路选择器,多个SI(进),一个MI(出),以及用于选路的控制信号。

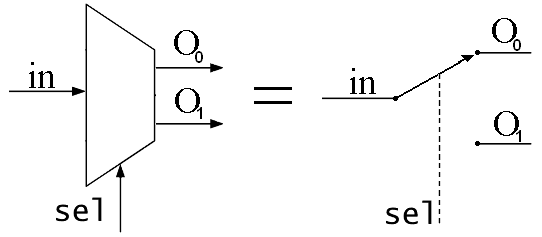

demux

demultiplexer,多路分配器,一个SI(进),多个MI(出),以及用于选路的控制信号。

仲裁算法(Vivado IP)

仲裁算法是针对多个S入口争用同一M出口时的问题。

- Round-Robin: 按端口数量分片,若当前端口没有任务,则将时间片顺延给下一个端口。

- True Round-Robin: 对所有active的端口进行等权值的时间分片。

- Fixed-Priority: 固定优先级调度,S00接口优先级最高,S15优先级最低。

cocotbext-axi 工具包的AXIS部分

AXIS部分中含有四个主要的类,AxiStreamSource, AxisStreamSink, AxisStreamMonitor and AxisStreamBus。